AD9516-3BCPZ IC zegar PLL/VCO 2GHZ 64LFCSP

Parametr produktu

Opis

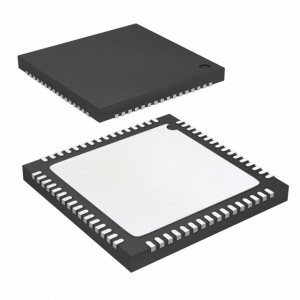

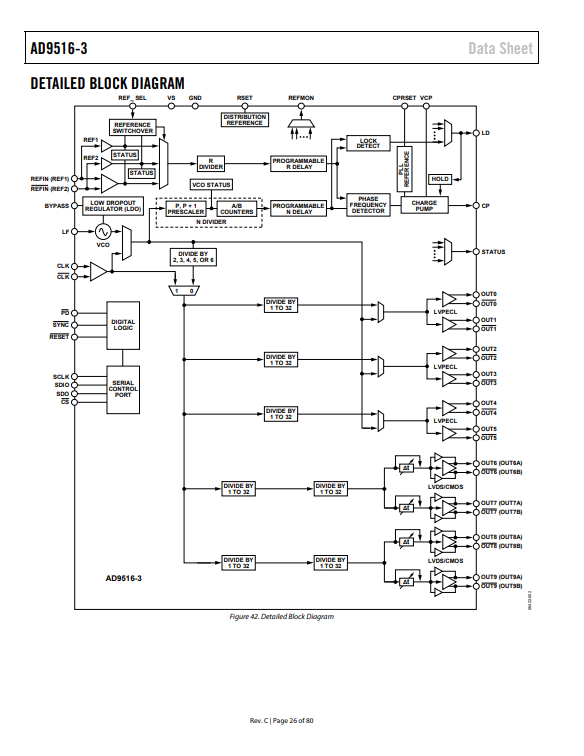

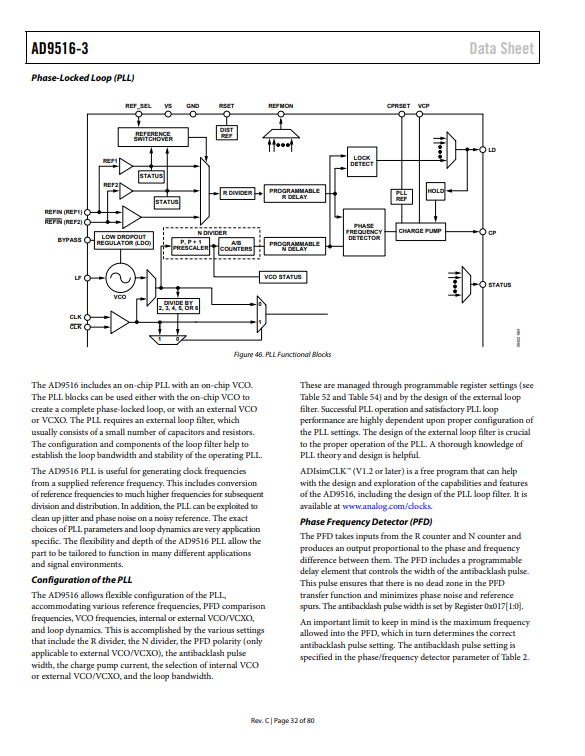

AD9516-31 zapewnia funkcję dystrybucji zegara z wieloma wyjściami z subpikosekundową wydajnością jittera, wraz z wbudowanym układem PLL i VCO.Wbudowany układ VCO dostraja się w zakresie od 1,75 GHz do 2,25 GHz.Opcjonalnie można zastosować zewnętrzne VCO/VCXO do 2,4 GHz.AD9516-3 kładzie nacisk na niski jitter i szum fazowy, aby zmaksymalizować wydajność konwertera danych, i może przynieść korzyści innym aplikacjom z wysokimi wymaganiami dotyczącymi szumu fazowego i jittera.SCHEMAT BLOKU FUNKCJONALNEGO REFIN REF1 REF2 CLK LF PRZEŁĄCZNIK I MONITOR ROZDZIELACZ PLL I MUX CP MONITOR STANU VCO LVPECL LVPECL LVPECL LVDS/CMOS LVDS/CMOS PORT STEROWANIA SZEREGOWEGO I LOGIKA CYFROWA AD9516-3 OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 VOUT8 OUT9 DIV/Φ DIV/Φ DIV/Φ DIV/Φ DIV/Φ DIV/Φ Δt Δt Δt Δt 06422-001 Rysunek 1. AD9516-3 posiada sześć wyjść LVPECL (w trzech parach) i cztery wyjścia LVDS (w dwóch parach) .Każde wyjście LVDS można skonfigurować jako dwa wyjścia CMOS.Wyjścia LVPECL działają z częstotliwością 1,6 GHz, wyjścia LVDS działają z częstotliwością 800 MHz, a wyjścia CMOS działają z częstotliwością 250 MHz.Każda para wyjść posiada dzielniki, które umożliwiają ustawienie zarówno współczynnika podziału, jak i zgrubnego opóźnienia (lub fazy).Zakres podziału dla wyjść LVPECL wynosi od 1 do 32. Wyjścia LVDS/CMOS umożliwiają zakres podziału do maksymalnie 1024. AD9516-3 jest dostępny w 64-odprowadzeniowym LFCSP i może być obsługiwany z jednego 3,3 dostawa V.Zewnętrzny VCO, który wymaga rozszerzonego zakresu napięcia, można podłączyć, podłączając zasilanie pompy ładującej (VCP) do 5 V. Oddzielny zasilacz LVPECL może mieć napięcie od 2,5 V do 3,3 V (nominalnie).AD9516-3 jest przeznaczony do pracy w standardowym zakresie przemysłowym od -40°C do +85°C.

| Dane techniczne: | |

| Atrybut | Wartość |

| Kategoria | Układy scalone (IC) |

| Zegar/Timing - generatory zegarowe, PLL, syntezatory częstotliwości | |

| Prod | Urządzenia analogowe Inc. |

| Seria | - |

| Pakiet | Taca |

| Stan części | Aktywny |

| Typ | Generator zegarów, dystrybucja fanoutów |

| PLL | Tak |

| Wejście | Zegar |

| Wyjście | CMOS, LVDS, LVPECL |

| Liczba obwodów | 1 |

| Stosunek — wejście: wyjście | 1:14 |

| Różnicowy — Wejście: Wyjście | Tak tak |

| Częstotliwość — maks | 2,95 GHz |

| Dzielnik/mnożnik | Tak nie |

| Napięcie zasilające | 3,135 V ~ 3,465 V |

| temperatura robocza | -40°C ~ 85°C |

| Typ mocowania | Montaż powierzchniowy |

| Opakowanie / Sprawa | 64-VFQFN Odsłonięta podkładka, CSP |

| Pakiet urządzeń dostawcy | 64-LFCSP-VQ (9x9) |

| Pakiet urządzeń dostawcy | 64-LFCSP-VQ (9x9) |

| Podstawowy numer produktu | AD9516 |

PowiązanyPRODUKTY

-

Tel

-

E-mail

-

skype

-

WhatsApp

WhatsApp