EP1C6Q240C8N IC FPGA 185 we/wy 240QFP

Parametr produktu

Opis

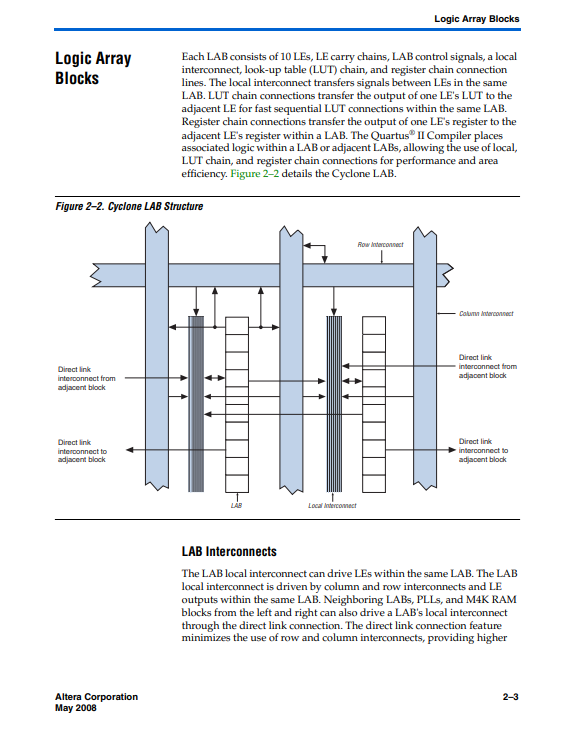

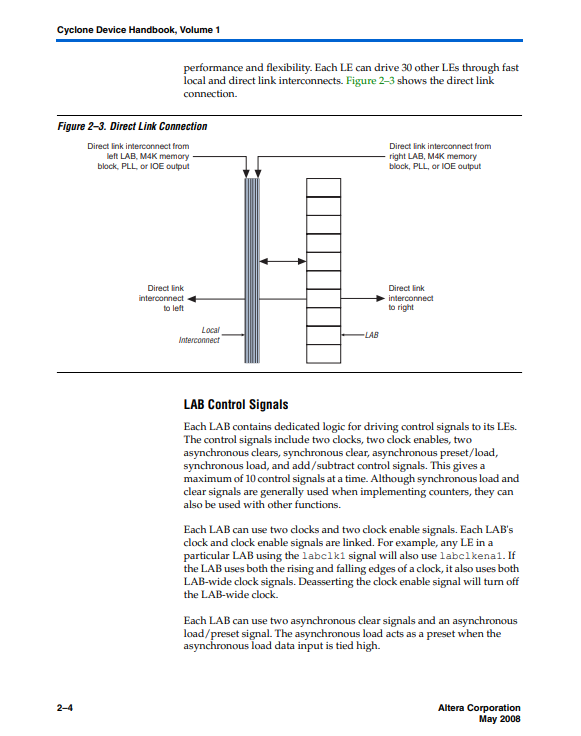

Urządzenia Cyclone® zawierają dwuwymiarową architekturę opartą na wierszach i kolumnach w celu wdrożenia niestandardowej logiki.Połączenia międzykolumnowe i rzędowe o różnych prędkościach zapewniają wzajemne połączenia sygnałowe między LAB i wbudowanymi blokami pamięci.Tablica logiczna składa się z LAB, z 10 LE w każdym LAB.LE to mała jednostka logiczna zapewniająca efektywną implementację funkcji logiki użytkownika.LAB są pogrupowane w wiersze i kolumny na całym urządzeniu.Urządzenia Cyclone mają zakres od 2910 do 20 060 LE.Bloki pamięci RAM M4K to prawdziwie dwuportowe bloki pamięci z 4K bitów pamięci plus parzystość (4608 bitów).Bloki te zapewniają dedykowaną pamięć dwuportową, prostą dwuportową lub jednoportową o szerokości do 36 bitów i częstotliwości do 250 MHz.Bloki te są pogrupowane w kolumny w całym urządzeniu pomiędzy określonymi LAB.Urządzenia Cyclone oferują od 60 do 288 Kbit wbudowanej pamięci RAM.Każdy pin wejścia/wyjścia urządzenia Cyclone jest zasilany przez element wejścia/wyjścia (IOE) umieszczony na końcach rzędów i kolumn LAB na obwodzie urządzenia.Piny we/wy obsługują różne standardy pojedynczych i różnicowych we/wy, takie jak 66- i 33-MHz, 64- i 32-bitowy standard PCI oraz standard we/wy LVDS z szybkością do 640 Mb/s.Każdy IOE zawiera dwukierunkowy bufor I/O i trzy rejestry do rejestrowania sygnałów wejściowych, wyjściowych i wyjściowych.Dwufunkcyjne piny DQS, DQ i DM wraz z łańcuchami opóźnień (używanymi do wyrównania faz sygnałów DDR) zapewniają obsługę interfejsów z zewnętrznymi urządzeniami pamięci, takimi jak urządzenia DDR SDRAM i FCRAM z szybkością do 133 MHz (266 Mb/s).Urządzenia Cyclone zapewniają globalną sieć zegarową i do dwóch PLL.Globalna sieć zegara składa się z ośmiu globalnych linii zegara, które poruszają się po całym urządzeniu.Globalna sieć zegarów może dostarczać zegary dla wszystkich zasobów w urządzeniu, takich jak IOE, LE i bloki pamięci.Linie zegara globalnego mogą być również używane jako sygnały sterujące.Cyclone PLL zapewniają taktowanie ogólnego przeznaczenia z mnożeniem zegara i przesunięciem fazowym, a także zewnętrzne wyjścia do obsługi szybkich różnicowych wejść/wyjść.

| Dane techniczne: | |

| Atrybut | Wartość |

| Kategoria | Układy scalone (IC) |

| Wbudowane — układy FPGA (programowalna przez użytkownika macierz bramek) | |

| Prod | Intel |

| Seria | Cyklon® |

| Pakiet | Taca |

| Stan części | Przestarzały |

| Liczba LAB/CLB | 598 |

| Liczba elementów logicznych/komórek | 5980 |

| Całkowita liczba bitów pamięci RAM | 92160 |

| Liczba wejść/wyjść | 185 |

| Napięcie zasilające | 1,425 V ~ 1,575 V |

| Typ mocowania | Montaż powierzchniowy |

| temperatura robocza | 0°C ~ 85°C (TJ) |

| Opakowanie / Sprawa | 240-BFQFP |

| Pakiet urządzeń dostawcy | 240-PQFP (32x32) |

| Podstawowy numer produktu | EP1C6 |

PowiązanyPRODUKTY

-

Tel

-

E-mail

-

skype

-

WhatsApp

WhatsApp